https://xtech.nikkei.com/atcl/nxt/column/18/00001/08857/

https://xtech.nikkei.com/atcl/nxt/column/18/00001/08857/

1nm世代プロセス以降の次世代半導体で使われるトランジスタ構造「CFET」。台湾積体電路製造(TSMC)や韓国Samsung Electronics(サムスン電子)など半導体製造の先頭を走る企業がこぞって研究し、Rapidus(ラピダス、東京・千代田)もフランスの半導体研究機関Letiと共同で取り組む。ところが、そこに意外な“落とし穴”が見えてきた。

「現状ではほとんどの論理回路が実現できない」。こう警鐘を鳴らすのは、湘南工科大学 名誉教授 兼 学事顧問の渡辺重佳氏である。CFETには回路設計上の課題があるからだ。そこで同氏は、CFETとは異なる、既存技術を応用した集積化を提案した。「ラピダスがこの技術を使えば、TSMCにも勝てるだろう」(同氏)と自信を見せる。

CFETは、現状最先端のトランジスタ構造であるGAA(Gate All Around) FETの次世代に当たる将来技術。現状はまだ前世代であるGAA構造の量産が始まった段階にある。サムスン電子は2022年、世界に先駆けてGAA構造の3nm世代半導体を製造開始し、量産にこぎ着けた。TSMCや米Intel(インテル)、ラピダスがその後を追う。

プレーナFET、FinFET、GAAナノシート、GAAフォークシート、CFET――。半導体素子であるトランジスタの構造は2000年代以降、微細化の継続のために変化し続けてきた注1)。ポイントは同じ面積にどれだけ多くのトランジスタ数を詰め込むかだ。単純に素子や配線を微細化するだけでは物理限界に達しつつあり、FinFET以降、垂直方向の面積を利用する技術が採用されている(図1)。

縦に積層して横幅を縮めたCFET

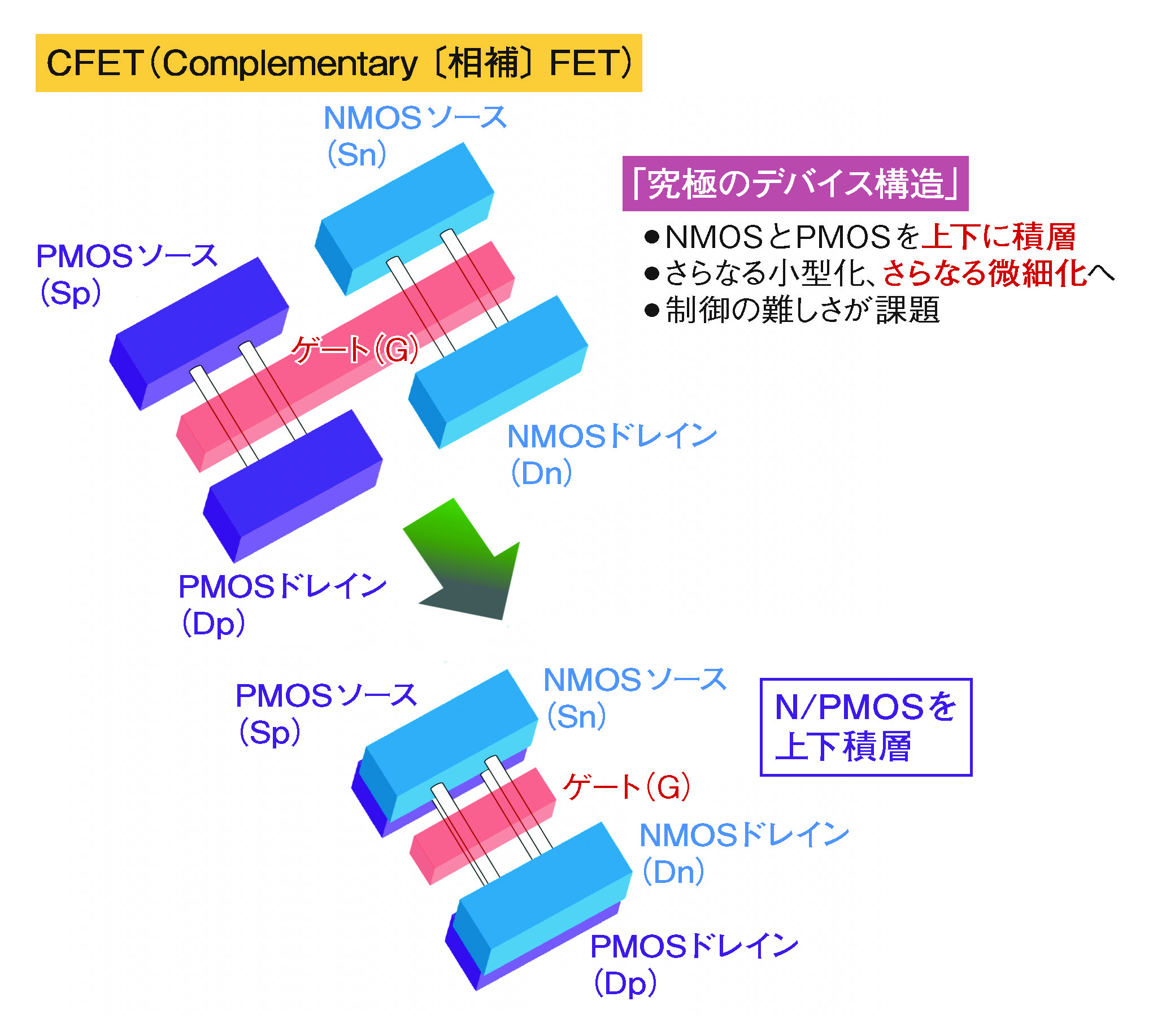

CFETの構造は、この3次元化をさらに進めるものだ。CMOSトランジスタはNMOSとPMOSで構成し、これらを組み合わせることで論理回路を形成している。CFETは、それまで横方向に並べていたNMOSとPMOSを上下に積層して一体化させた。トランジスタの横幅を大幅に縮小し、さらなる集積化につなげる狙いである(図2)。

「トランジスタにおける究極のデバイス構造」。ベルギーの半導体研究機関imecでSTS/CMOST/TSE プログラムディレクターを務める堀口直人氏はCFETをこう称する。imecのロードマップでは2032年に仮の実現時期を置き、プロセスノードを5Å(オングストローム、1Åは0.1nm)世代以降まで継続できるとする。

GAA FETの先にある目標地点として、各社はこぞってCFETを研究する。だが、そんな状況に疑問符を投げかける半導体研究者が現れた。

0 件のコメント:

コメントを投稿