https://eetimes.itmedia.co.jp/ee/articles/2312/19/news079.html

https://eetimes.itmedia.co.jp/ee/articles/2312/19/news079.html

(1/2 ページ)

今回は初期の「FO-WLP」で生じた信頼性の問題と、問題を解決した組み立てプロセス、再配線層(RDL)を微細化したプロセスを解説する。

「FO-WLP」の信頼性問題

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

本コラムの第433回から、第3章「電子デバイスパッケージ」の第3節(3.3)「各種パッケージ技術動向」を報告してきた。前々回は第3章第3節第2項(3.3.2)「ウェハレベルパッケージ(WLP)、パネルレベルパッケージ(PLP)、部品内蔵基板」から、「3.3.2.1 WL-CSP(Wafer Level-Chip Size Package)」の概要を説明した。続く前回は、「3.3.2.2 FO-WLP(Fan Out-Wafer Level Package)、FO-PLP(Fan Out-Panel Level Package)、部品内蔵基板」の概要(前半部分)をご報告した。

今回は初期の「FO-WLP」で生じた信頼性の問題と、問題を解決した組み立てプロセス、それから再配線層(RDL)を微細化したプロセスをご説明する。

シリコンと樹脂の熱膨張率の違いが応力集中を引き起こす

初期の「FO-WLP」で生じた信頼性問題は、シリコンダイとモールド樹脂の熱膨張率の違いに起因する。シリコンの熱膨張係数は室温付近で約2.6ppm/℃であるのに対し、モールド樹脂(エポキシ樹脂)の熱膨張係数は30~40ppm/℃前後とされる。10倍を超える違いがあることが分かる。

シリコンダイの動作発熱や外的環境の寒暖差などの温度変化によってシリコンダイとモールド樹脂の境界では、機械的な応力が発生する。FO-WLPの場合、境界付近のRDL絶縁層とRDL(配線層)が延びたり縮んだりする。場合によっては絶縁層や配線層などにクラックが入りかねない。

そこでシリコンダイの電極に銅(Cu)バンプを形成することで、ダイの表面をモールド樹脂で覆い、RLD絶縁層を境界面から離す構造が開発された。既に実用化されている。

「FO-WLP」で生じた信頼性問題とその対策。左(a)は初期のFO-WLPにおけるシリコンダイとモード樹脂の境界付近の断面構造図。シリコンダイとモールド樹脂の境界では、温度変化によって機械的な応力が発生する(図中の黄色い円)。この機械的な応力がRDL領域を伸縮させ、場合によってはクラックに至る。右(b)は対策を施した構造の断面図。シリコンダイ表面に銅(Cu)バンプを形成しておくことで、RDL領域をシリコンダイから離す。応力が発生してもRDL領域には影響しない[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

「FO-WLP」で生じた信頼性問題とその対策。左(a)は初期のFO-WLPにおけるシリコンダイとモード樹脂の境界付近の断面構造図。シリコンダイとモールド樹脂の境界では、温度変化によって機械的な応力が発生する(図中の黄色い円)。この機械的な応力がRDL領域を伸縮させ、場合によってはクラックに至る。右(b)は対策を施した構造の断面図。シリコンダイ表面に銅(Cu)バンプを形成しておくことで、RDL領域をシリコンダイから離す。応力が発生してもRDL領域には影響しない[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)シリコンダイ表面に銅バンプをあらかじめ形成

上述の対策を施したFO-WLPの組み立て工程を説明しよう。「チップファースト」かつ「フェースアップ」のプロセスである。始めは、回路と銅バンプを形成済みのシリコンウエハーを裏面から所望の厚さになるまで研削し、個々のシリコンダイに切り離す。

それからキャリア(表面にはあらかじめ粘着フィルムが貼ってある)にシリコンダイ(チップ)をフェースアップで再配置する。それからキャリアのシリコンダイ側をモールド樹脂で封止する。

次にモールド樹脂を研削し、シリコンダイの銅バンプを露出させたところで研削を止める。続いてシリコンダイ表面側(銅バンプ側)に、再配線層(RDL)の誘電体層と配線層を形成する。RDLが完成した後は、モールド樹脂の疑似ウエハーからキャリアをはく離する。

ここで疑似ウエハーを裏面から研削して薄型化することもある。その場合は裏面を保護する樹脂フィルムを貼る。それから表面電極にはんだボール(外部端子)を搭載する。最後に個々のパッケージに切り離す(個片化)。

信頼性問題に対策を施した「FO-WLP」の組み立て工程[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)

信頼性問題に対策を施した「FO-WLP」の組み立て工程[クリックで拡大] 出所:JEITA Jisso技術ロードマップ専門委員会(2022年7月7日に開催された完成報告会のスライド)平坦なキャリアによってRDLを微細化

ここまで述べてきたFO-WLPのRDLは配線幅/間隔が最小でも10μm/10μmであり、製造歩留まりを考慮すると15~20μm/15~20μmで量産することが多い。この配線幅/間隔はあまり微細とはいえず、ピン数が1000ピンを超えるシングルチップあるいはマルチチップのパッケージではRDLの配線引き回しが難しくなる。

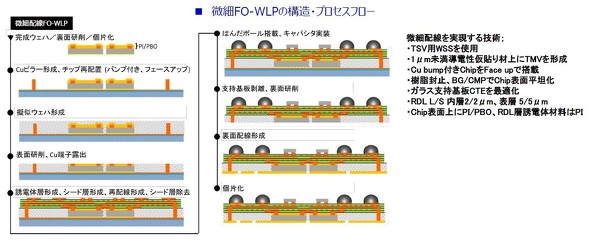

そこで1000ピン~2000ピンの超多ピンに対応すべく開発されたのが、微細配線を有するFO-WLPである。代表的な応用例はスマートフォンのアプリケーションプロセッサで、ピン数は2000ピン弱に及ぶ。

微細配線を有するFO-WLPのRDL配線幅/間隔は2~5μm/2~5μmと狭い。このような微細化を可能にしたのは、下地である疑似ウエハーの平坦(へいたん)度を確保したことにある。具体的には、平坦度が高く、かつ熱膨張係数がシリコンダイに近いガラス製のキャリアを採用するとともに、ガラスキャリアの表面に薄い導電接着膜を形成した。

組み立て工程そのものは「チップファースト」かつ「フェースアップ」で進む。回路形成済みウエハーの回路側に銅バンプ(Cuバンプ)とポリイミド(PI)/ポリベンゾオキサゾール(PBO)誘電体層を形成し、個々のシリコンダイに切り離す。切り離したシリコンダイをキャリアにフェースアップで搭載する。なお、キャリアにはあらかじめ銅の柱(Cuピラー)を形成してある。

シリコンダイとCuピラーを覆うようにモールド樹脂で封止して疑似ウエハーを形成し、モールド樹脂表面を研削してCuピラーとシリコンダイのCuバンプを露出させる。続いてRDL層を形成する。それからはんだボールとキャパシターを搭載する。キャリアをはく離して裏面を研削し、裏面に配線を形成する(パッケージオンパッケージの場合)。最後に個々のパッケージに切り離す。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

0 件のコメント:

コメントを投稿