https://eetimes.itmedia.co.jp/ee/articles/2312/22/news058.html

https://eetimes.itmedia.co.jp/ee/articles/2312/22/news058.html

(1/2 ページ)

今回は、FO-WLP(Fan Out-Wafer Level Package)のロードマップと、FO-PLP(Fan Out-Panel Level Package)の一種ともみなせる部品内蔵基板について解説する。

FO-WLPのロードマップを2031年まで示す

電子情報技術産業協会(JEITA)が3年ぶりに実装技術ロードマップを更新し、「2022年度版 実装技術ロードマップ」(書籍)を2022年7月に発行した。本コラムではロードマップの策定を担当したJEITA Jisso技術ロードマップ専門委員会の協力を得て、ロードマップの概要を本コラムの第377回からシリーズで紹介している。

本コラムの第433回から、第3章「電子デバイスパッケージ」の第3節(3.3)「各種パッケージ技術動向」を報告してきた。前々回と前回は、第3章第3節第2項(3.3.2)「ウェハレベルパッケージ(WLP)、パネルレベルパッケージ(PLP)、部品内蔵基板」の第2項目「3.3.2.2 FO-WLP(Fan Out-Wafer Level Package)、FO-PLP(Fan Out-Panel Level Package)、部品内蔵基板」の概要をご説明した。今回は説明の続きとなる。

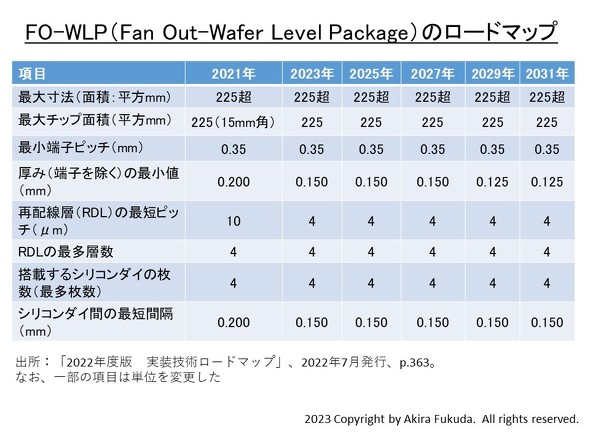

はじめに、FO-WLPのロードマップを示したい。2021年から2031年までの10年間を2年ごとに推定あるいは予測した。全体としては変化が少ない。厚みが0.200mmから0.125mmへと薄くなり、再配線層(RDL)の配線ピッチが10μmから4μmへと短くなり、シリコンダイ間の間隔が0.20mmから0.15mmへと短くなる。

ウエハーよりも大きなプリント基板によって製造コストをさらに下げる

続いて「部品内蔵基板」のご説明に移ろう。部品内蔵基板とは名称の通り、半導体チップ(シリコンダイ)や電子部品などを内蔵したプリント基板を意味する。半導体パッケージとしての部品内蔵基板のメリットは、シリコンウエハーよりも大きなプリント基板を使った、パッケージング工程の一括処理が可能なことにある。原理的にはウエハーレベルのパッケージングよりもパッケージ当たりのコストが下がる。

シリコンウエハーの最大寸法は直径300mmである。ウエハーは円形なので、正方形に換算すると213mm角になる。一方、部品内蔵基板の製造で利用する代表的なプリント基板(矩形)の寸法は、400mm×300mm、500mm角、700mm×500mmとシリコンウエハーの2倍以上の寸法がある。面積としては4倍を超える。

パッケージ技術としての部品内蔵基板は、パネルレベルパッケージ(PLP)の一種ともみなせる。「FO-PLP(Fan Out-Panel Level Package)」は矩形のパネル(通常はプリント基板)を扱うので、FO-PLPの中でプリント基板にシリコンダイを内蔵するタイプが「部品内蔵基板」だとも言える。後述する微細配線を形成可能なタイプは「部品内蔵基板」ではなく、「FO-PLP」と表記されることが多い。

プリプレグと銅箔の組み合わせで部品内蔵基板を作成

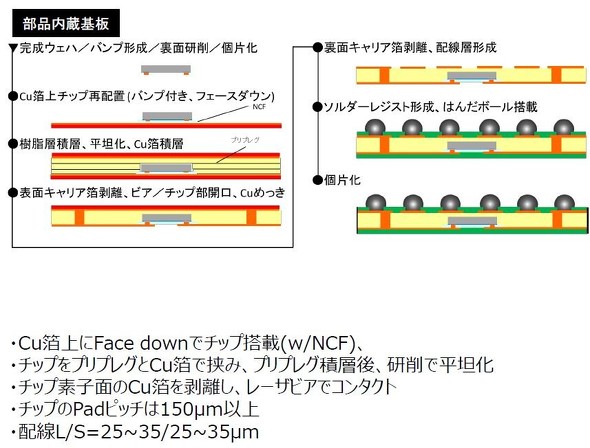

代表的な部品内蔵基板(パッケージ)は、多層プリント基板の素材であるプリプレグ(樹脂シート)を複数枚積層したコアと、コアの両面に形成した銅箔(Cu箔)によって構成される。組み立て工程を以下に説明しよう。「チップファースト」「フェースダウン」の工程である。

回路形成と銅(Cu)バンプ形成を完了したシリコンウエハーを目的の厚みまで裏面研削し、それから個々のシリコンダイに分離する(個片化)。キャリアは厚い銅箔(Cu)である。厚いCu箔の上に薄いCu箔(配線形成用)を積層する。それから非導電フィルム(NCF:Non Conductive Film)を薄いCu箔表面の一部に載せ、その上にシリコンダイをマウントする。

次に、シリコンダイに当たる部分にあらかじめ穴を開けてあるプリプレグを複数枚、Cuキャリアに載せてプレスし、最上層を平坦(平たん)化(研削)する。プリプレグの最上層に、配線用の薄いCu箔とキャリア用の厚いCu箔を貼り合わせる。なお薄いCu箔の厚みは18μm以下である。

それから、シリコンダイの回路側(フェース側)のキャリア用Cu箔をはく離し、レーザードリルによってシリコンダイとCuバンプの領域、両面貫通ビア領域の薄いCu箔に穴を開ける。CuめっきによってCuバンプとCu箔を接続するとともに貫通ビアをCuで埋める。

続いてシリコンダイの裏面側のキャリア用Cu箔をはく離し、配線層を形成する。さらにソルダーレジスト(保護膜を兼ねる)を形成し、はんだボール(外部電極)を搭載する。最後に、基板を個々のパッケージに分割する(個片化)。

上記の部品内蔵基板では、配線の線幅と間隔は最短25μm/25μmとFO-WLPの最短10μm/10μmに比べて広い。シリコンダイのパッド(バンプ)ピッチは150μm以上、厚み(裏面研削後)は100μm~400μmである。

ガラス・エポキシ基板とガラスキャリアで微細な配線を実現

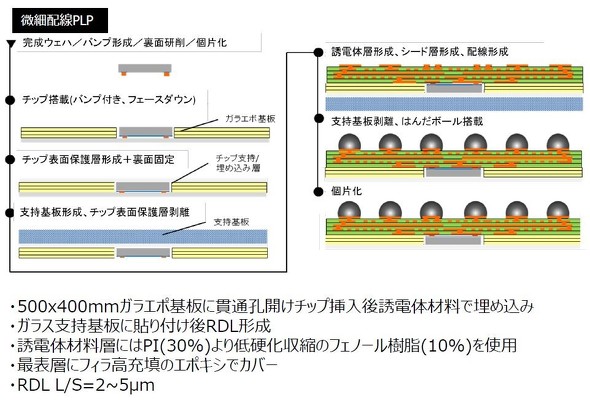

FO-WLPと同様に、部品内蔵基板でも微細な配線を形成可能な組み立てプロセスが存在する。以下に工程を説明しよう。「チップファースト」「フェースダウン」の工程である。

シリコンダイは銅(Cu)バンプ形成と裏面研削を完了後のウエハーから、個々に切り出す(個片化)。コアとなるプリント基板は大きさが500mm×400mm程度のガラス・エポキシ(ガラエポ)基板である。シリコンダイを載せる部分には、あらかじめ開口部(キャビティ)を作ってある。仮置き材(基板)とガラエポ基板を貼り合わせたコアのキャビティに、シリコンダイをフェースダウンで搭載する。続いてシリコンダイの側面と裏面を誘電体材料によって埋め込み、シリコンダイを固定する。

次にガラス製のキャリアを裏面に貼り付ける。ガラスを使うのは微細配線を形成可能な平坦度を確保するためである。キャリアを利用してシリコンダイの表面側に再配線層(RDL)を形成する。配線の線幅と間隔は2~5μm/2~5μmとかなり狭い。

RDLの誘電体層(絶縁層)にはポリイミドではなく、フェノール系樹脂を使う。ポリイミドは硬化収縮率が30%前後と大きく、反りの問題が発生する懸念が大きい。フェノール系樹脂は硬化収縮率が10%前後と小さく、反りの懸念が少ない。

RDLの形成後はキャリアをはく離し、はんだボールをRDLの上に搭載する。最後にガラエポ基板を個々のパッケージに分割する(個片化)。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

多ピン小型パッケージ「FO-WLP」の信頼性問題とその対策

多ピン小型パッケージ「FO-WLP」の信頼性問題とその対策 超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP

超多ピンと複数ダイ搭載を両立させた小型パッケージFO-WLP 表面実装工程の省エネに寄与する低融点の鉛フリーはんだ

表面実装工程の省エネに寄与する低融点の鉛フリーはんだ エレクトロニクスの進化を後押しする接合技術

エレクトロニクスの進化を後押しする接合技術 コンピューティングと計測・センシングの限界を打破する量子技術(前編)

コンピューティングと計測・センシングの限界を打破する量子技術(前編) 複数のガス分子を選択的に検出する「におい」センサー

複数のガス分子を選択的に検出する「におい」センサー

0 件のコメント:

コメントを投稿