https://news.mynavi.jp/techplus/article/20240501-2937991/

目次

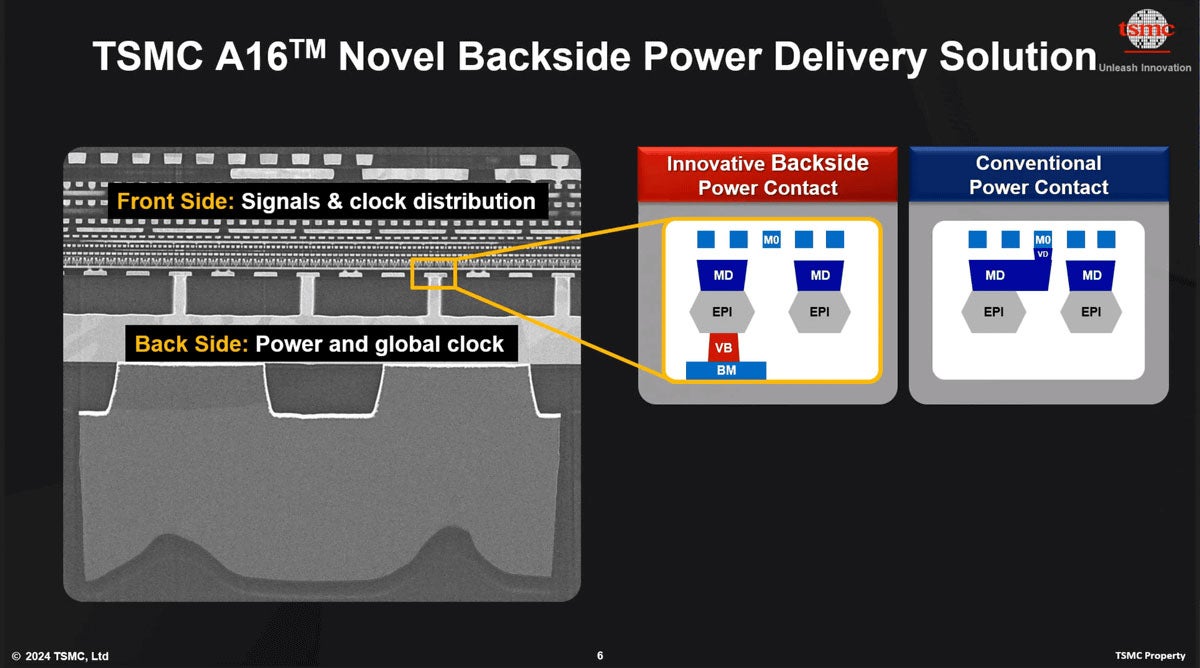

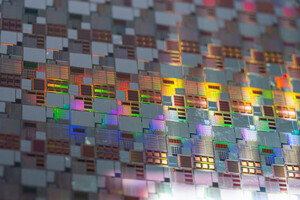

TSMCは4月24日、米国カリフォルニア州サンタクララで「North America Technology Symposium」を開催し、2026年の生産に向けて裏面パワーレール(裏面電源供給)を備えたナノシートトランジスタ(Gate-All-Around FET)を特徴とする「TSMC A16テクノロジー」を発表した。

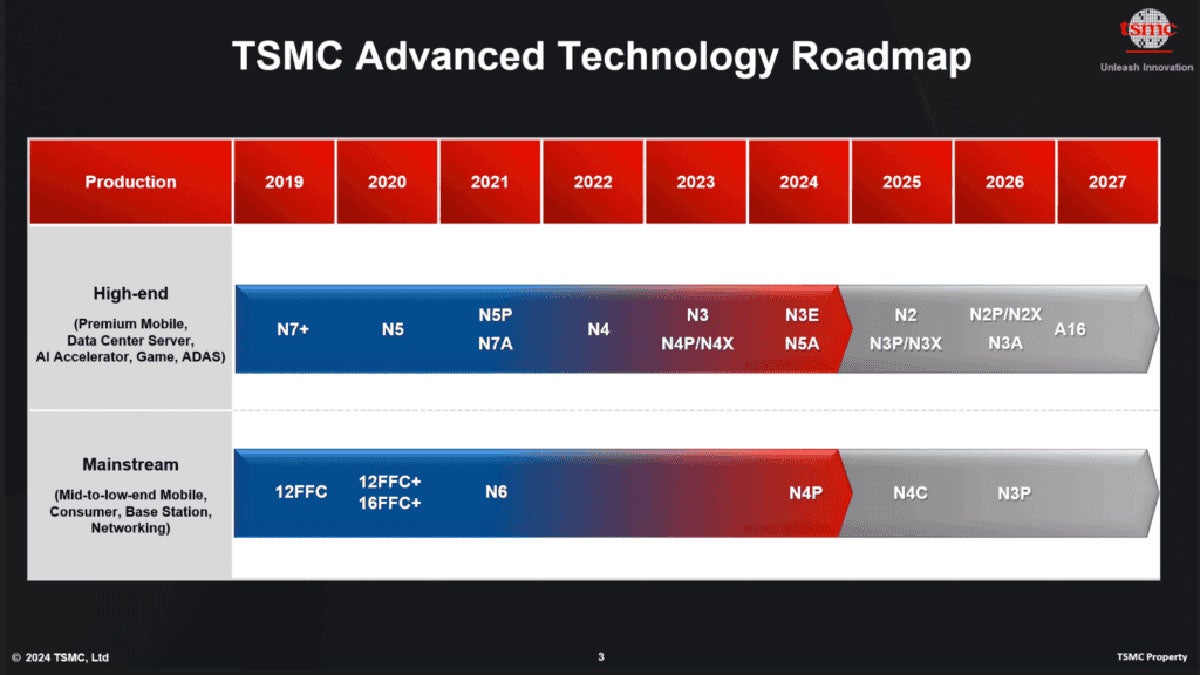

これまで同社は各プロセスの名称をN+数値と表記してきたが、今回から「N1.6」とはせず「A16」とオングストロームのAと数値へと呼称を変更した模様で、Samsung Electronicsが2027年に量産開始を予定している「SF1.4」やIntelが2026年に市場投入を予定している「Intel 14A」と競合することになる。

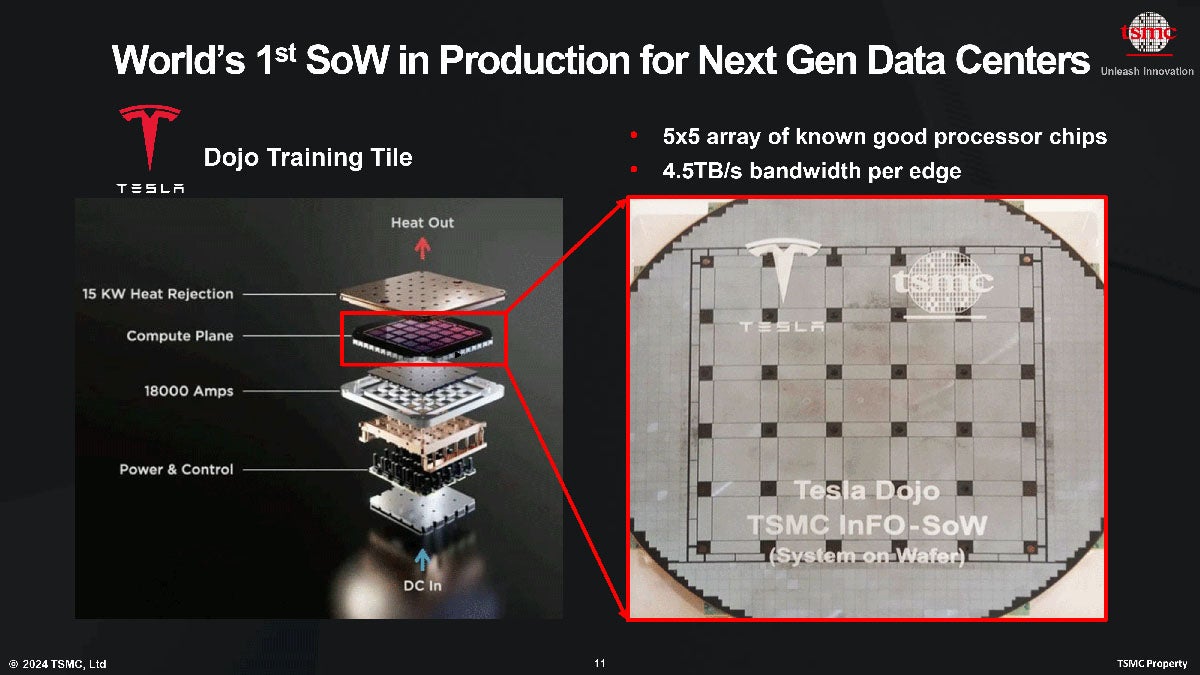

また、同シンポジウムにて同社はハイパースケーラー データセンターの将来のAI要件に対応可能な高性能パフォーマンスをウェハレベルにてもたらすソリューション「System on Wafer(TSMC-SoW)」やデータ伝送量の爆発的な増加を支援する独自のシリコンフォトニクス(光電融合)技術「COUPE」なども発表している。

TSMC A16テクノロジー

同社は現在、3nmプロセスの拡張版である「N3E」の量産を進めており、2025年後半には2mnプロセス「N2」の生産開始を予定している。A16は、その先のプロセスとして位置付けられるもので、2026年の生産に向けて同社のスーパーパワーレール(裏面電源供給)アーキテクチャとGAA FETが組み合わされる予定である。

裏面電源供給技術により、フロントサイドの配線リソースを信号専用にすることができ、ロジック密度とパフォーマンスが向上するため、複雑な信号処理と高密度の電力供給ネットワークが必要なHPCなどに最適だと同社では説明しており、同社のN2Pプロセスと比較して同じVdd(電源電圧)で8~10%の速度向上、同じ速度で15~20%の電力削減、データセンター製品のチップ密度の最大1.10倍の向上を実現するとしている。

また同社ではA16については高価な高NA EUV露光装置は採用しないとしており、まずはAIデータセンターなどスマートフォン(スマホ)以外の顧客が採用する可能性があるとしている。

ナノシートトランジスタに向けた新技術「TSMC NanoFlex」

TSMCの次期N2テクノロジーには、設計・テクノロジーの同時最適化における次世代技術となる「TSMC NanoFlex 」が採用されるという。この技術は、チップ設計の基本構成要素であるN2標準セルの柔軟性を設計者に提供する。ショートセルは狭い面積と優れた電力効率を強調し、トールセルはパフォーマンスを最大化する。顧客は、同じ設計ブロック内のショートセルとトールセルの組み合わせを最適化し、アプリケーションに最適な電力、性能、面積のトレードオフを達成するように設計を調整できるようになるという。

4nmプロセスの拡張版「N4Cテクノロジ」

TSMCでは先端技術をより幅広いアプリケーションに提供することを目指して、ダイコストを最大8.5%削減するN4Pテクノロジーの拡張版「N4C」を2025年に量産提供することも明らかにした。すでに広範に活用されているN4Pと完全互換のIPおよびデザインルールであり、面積効率が高く、ダイサイズの縮小による歩留まり向上が期待できるとしている。

新たな実装技術「TSMC-SoW」

TSMCの「Chip on Wafer on Substrate(CoWoS)」は、顧客がより多くのプロセッサコアと高帯域幅メモリ(HBM)をインターポーザー上に並べて搭載できるようにすることでAIが求める高い性能を実現した。一方の「System on Integrated Chips(SoIC)」は、3Dチップスタッキングの主要ソリューションとして活用されており、究極のシステムインパッケージ(SiP)の実現に向け、顧客はCoWoSとSoIC、その他のコンポーネントと組み合わせる案件が増えているという。

SoWは、300mmウェハ上に多数のダイを搭載できる新たなオプションとして提供されるもので、これによりデータセンターにおけるチップが占有する面積を削減させつつ、より多くの計算能力と消費電力あたりのパフォーマンスを向上させることを可能にすると同社では説明している。第1弾製品となる統合ファンアウト(InFO)テクノロジーに基づくロジック専用ウェハは、すでに生産が進められているほか、CoWoSを活用したChip on Waferバージョンも2027年に完成する予定で、SoIC、HBM、その他のコンポーネントを統合することで、データセンターのサーバーラック、さらにはサーバー全体に匹敵するコンピューティング能力を備えた強力なウェハレベルシステムの実現につなげるとしている。

シリコンフォトニクスの統合

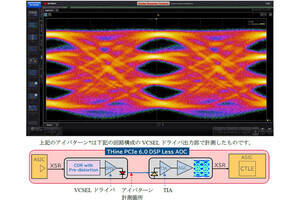

AIの爆発的な普及は、クラウドとエッジでやり取りするデータ量の爆発的な増加をもたらしている。この問題に対応することを目的に同社は「Compact Universal Photonic Engine(COUPE)」テクノロジーの開発を進めていることを明らかにした。

COUPEは、SoIC-Xチップスタッキングテクノロジーを使用することでフォトニックダイの上に電気ダイをスタック。ダイ間インタフェースのインピーダンスを低くすることで、従来スタッキング手法に比べて高いエネルギー効率を実現するという。

2025年にCOUPEをSFP(Small Form-factor Pluggables)の認定を受け、2026年にコ・パッケージ・オプティクス(CPO)としてCoWoSパッケージに統合し、パッケージに光接続を直接導入する予定だとしている。

自動車向け先端パッケージング技術も進化

TSMCは2023年、「N3AE Auto Early」プロセスを導入し、高度なシリコンチップと高度なパッケージングを統合することで、自動車の安全性と品質要求を満たす取り組みを進めてきた。次世代技術として同社では、2025年第4四半期までにAEC-Q100 Grade 2の認定取得を目指し、先進運転支援システム(ADAS)、車両制御、車両中央コンピューターなどのアプリケーションに向けて「InFO-oS(InFO on Substrate)」および「CoWoS-R(CoWoS-RDL interposer)」ソリューションを開発していることを明らかにした。

関連リンク

※本記事は掲載時点の情報であり、最新のものとは異なる場合があります。予めご了承ください。

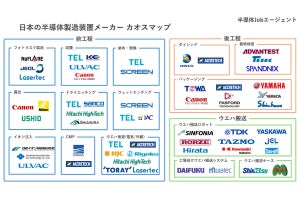

日本の半導体製造装置メーカーのカオスマップ、半導体Jobエージェントが公開

18時間前

インテルがソニー「PlayStation 6」のチップ契約を逃す - AMDが受注2024/09/17 14:21

インテルがソニー「PlayStation 6」のチップ契約を逃す - AMDが受注2024/09/17 14:21

Samsungの2/3nmの歩留まりが低迷、ファウンドリ事業を見直しか? 韓台メディア報道

2024/09/17 12:09

Intelが欧州2工場の建設を2年延期、Altera株式の一部も売却

2024/09/18 10:03

2024年第2四半期のNAND市場は出荷量が鈍化もAI需要で売り上げは拡大、TrendForce調べ

2024/09/17 17:09

このカテゴリーについて

インテルや東芝といった半導体メーカーや、CPU、メモリなどの半導体デバイスに関わる情報、市場トレンドといったホットなニュースを毎日更新。注目のIoTや自動運転など、半導体の適用範囲の拡大とともに成長が続く半導体業界の話題を詳細な説明付きで紹介します。

0 コメント:

コメントを投稿