https://xtech.nikkei.com/atcl/nxt/column/18/00001/08757/

https://xtech.nikkei.com/atcl/nxt/column/18/00001/08757/

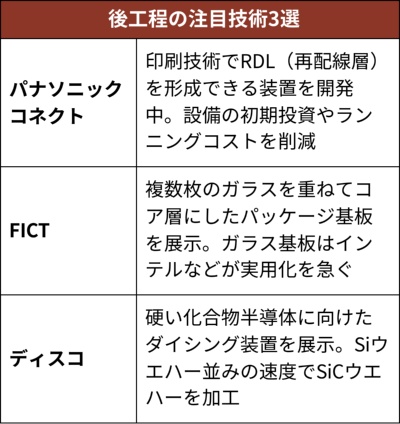

半導体後工程への関心が急速に高まっている。2023年12月に開催された専門イベント「SEMICON Japan 2023」では、後工程に特化した展示フロア「APCS」の面積が前年の1.4倍に拡大するなど、新技術を求める動きが活発だ。本稿では、注目すべき3つの技術を取り上げる。

印刷技術でRDL形成

パナソニックホールディングス傘下のパナソニックコネクトは、開発中の「高精度・加熱インプリント装置」を展示した。印刷技術を使って、銅(Cu)と絶縁層から成る「再配線層(RDL)」を形成できる。2.5次元実装向けの技術だ。同社の試算によるとRDL形成に関わる設備の初期投資を3割、運用コスト(ランニングコスト)を2割削減できるという。

インプリント装置では、微細な加工を施した型を加工対象に押し付け、加熱などの処理でパターンを形成する。開発中の装置は、プリントヘッドと荷重ヘッドが分離した構造を採用することで、プリントヘッド先端のぶれを0.1μm以下に抑制できた。

加工事例として、9.5μmの厚さのウエハーに直径2μm、高さ8μmの穴を開けた事例を披露した。RDLだけではなく、微細バンプの形成などにも適用できるという。微細配線とビアの一括形成も可能だ。

多層コアのガラス基板

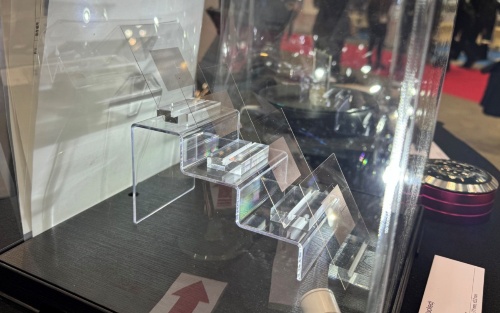

パッケージ基板を手がけるFICT(長野市、旧富士通インターコネクトテクノロジーズ)は、ガラスコアを使ったパッケージ基板を展示した。ガラスコアのパッケージ基板は、基板上に配置する電極のピッチを従来の樹脂基板よりも密にできることから期待されている技術だ。例えば、米Intel(インテル)などが実用化に向けて技術開発に力を注いでいる。

FICTが展示したパッケージ基板の特徴は、複数枚のガラスから成るコア層だ。厚さ100μmのガラス層と10μmの絶縁層、5μm銅箔を何枚も貼り合わせた。

ガラスコアを多層とすることで、単層の場合と比べて内部応力に対して強くなる。単層のガラスコアでは、基板の端などに強い応力がかかってしまい、破損や変形などを引き起こすことがあった。多層であれば、応力を均等に分散できる。単層の場合に強い応力がかかっていた部分でも、多層では応力を5分の1に抑えられるという。

化合物半導体の加工時間を10分の1に

後工程のダイシング装置で世界最大手のディスコは、炭化ケイ素(SiC)などの硬い化合物半導体に向けたダイシング装置「DDS2020」を展示した。別のレーザー加工装置と組み合わせることで、ダイシングにかかる時間を従来の10分の1に短縮できるという。

DDS2020では、レーザーを加工対象の内部に集光することで照射箇所に改質層を形成し、外部応力を加えてチップ分割を行う手法を採用した。シリコン(Si)の場合は比較的小さな力でチップを分割できるが、SiCウエハーなどは機械的強度が高い。今後のSiC普及を見据えて、新しい機構を開発した。

SiCなどの化合物半導体は、Siに比べてダイシングに時間がかかっていた。DDS2020を使えば、Si並みの加工速度が見込めるとしている。

0 コメント:

コメントを投稿