https://xtech.nikkei.com/atcl/nxt/column/18/02748/032400006/

https://xtech.nikkei.com/atcl/nxt/column/18/02748/032400006/

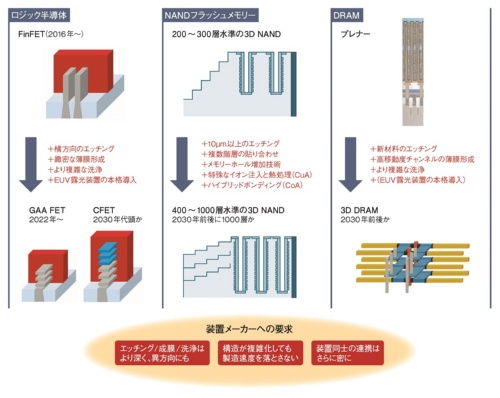

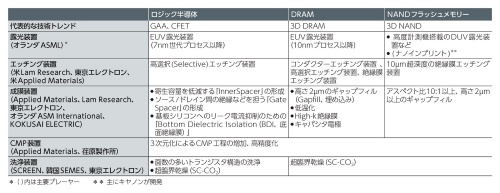

半導体製造は今、「デバイス構造の3次元化」という共通課題に直面している。先端品がそろって垂直方向の面積利用に集積化の活路を見出したからだ。複雑な3次元構造を、いかに欠陥なく、高精度に、速く製造できるか。製造装置メーカーへの要求は難解を極める(図1)。

半導体は、同じ面積に集積できるトランジスタやメモリーセルの素子の数を増やすべく進化してきた。素子を多くする利点は多い。電子機器の「頭脳」を担うロジック半導体は、トランジスタを増やすことで計算能力を上げられる。「記憶」を担う半導体メモリーは、同じ面積であっても記憶容量を向上できる。さらに、素子当たりの製造コストを下げられる注1)。

しかし、ロジック半導体でも半導体メモリーでも、従来と同じ方法で水平面に「詰め込む」微細化には限界が見えている。そこで今度は垂直面に「積み上げる」集積化という構造変化が起こっている。

先端ロジック半導体の最前線は、第1段階の3次元構造であるFinFETから、新たなトランジスタ構造であるGAA FET(Gate All Around Field Effect Transistor)に移行した。号砲になったのは、2022年の韓国Samsung Electronics(サムスン電子)による量産開始だ注2)。台湾TSMC(台湾積体電路製造)や米Intel(インテル)、Rapidus(ラピダス、東京・千代田)が量産に挑む。

先端半導体メモリーでは、NANDフラッシュメモリー(以下、「NAND」)で既に200層程度の3次元化が当たり前になり、さらに困難な400層以上の多層化に挑む。DRAM はまだ2次元構造であるものの、近い将来の3次元化が待ったなしの状況である。

製造装置メーカーにとっては、こうした複雑な3次元構造の形成は、半導体製造企業からの新たな“挑戦状”だ。求められているのは精密さだけではない。従来の構造と比べて製造速度を落とさない工夫も必要だからである(図2)。

「人工知能(AI)関連での需要などから、多少コストが高くとも、少しでも早く製造したいという要望が多くある。ただ、先端半導体の製造には精密さが必要で、(各工程の加工に)時間がかかる」と東京エレクトロン コーポレートオフィサー専務執行役員 SPE事業本部長の三田野好伸氏は話す。「さまざまな工夫をして、製造速度が落ちないようにすることが重要だ」(同氏)と述べる(図3)。

ナノシート構造で「横方向の加工」ニーズ

先端ロジック半導体は、精密な加工に伴う新たな半導体製造装置のニーズを生み出している。従来のプレナーやFinFETに比べて、GAA FETがより複雑な構造だからだ。

半導体製造は今、「デバイス構造の3次元化」という共通課題に直面している。先端半導体がそろって垂直方向の面積利用に集積化の活路を見出したからだ。複雑な3次元構造を、いかに欠陥なく、高精度に、速く製造できるか。製造装置メーカーへの要求は難解を極める。

0 コメント:

コメントを投稿