https://www.nikkei.com/prime/tech-foresight/article/DGXZQOUC06AJG0W4A200C2000000?n_cid=NPMTF000P_20240207_a15

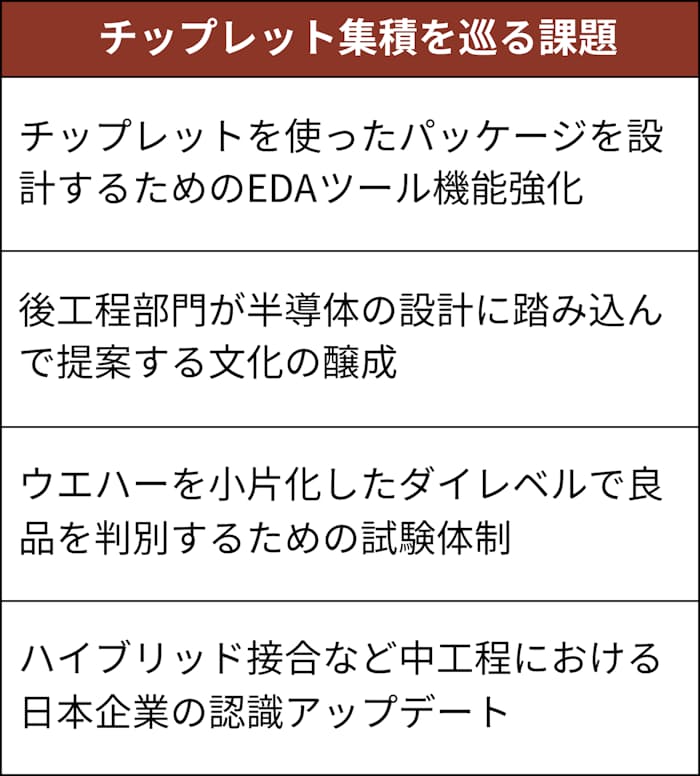

半導体の性能を高める上で、微細化に代わるアプローチとしてチップレット集積(異種チップ集積)などの先進後工程(先進パッケージング)への期待が高まっている。だが、普及に向けた課題は多い。

例えば、チップレット集積の理想形は半導体メーカーの枠を超えてユーザーが最適なチップレットを選定し、半導体パッケージを自由に開発できることだ。しかし、現在は半導体メーカーがチップレットの選定を含めたパッケージの企画や製品化を手がけ、ユーザーは限られた種類からチップを選ぶしかない。開発環境でいえば、複数のチップレットと基板を確認しながら一元的に設計できるツールはまだ少ない。国際競争の観点からは、先進パッケージングに全世界から多くの関心と投資が集まるようになったことで、これまでリードしていた日本企業が技術開発で後れを取る分野も出てきた。

このようなチップレットを巡る課題をどう解決していけばよいのか。チップレットの最前線を知る企業や大学のキーパーソンが、2023年12月開催の「SEMICON Japan 2023」内の先進パッケージ専門イベント「Advanced Packaging and Chiplet Summit(APCS)」で議論した。

EDAの機能強化が急務

前述した通り、チップレット集積の理想形はユーザーが様々なメーカーのチップレットを自由に組み合わせてパッケージを開発する「オープンチップレット」だ。しかし、現在のチップレット集積では、パッケージ全体をトップダウンで設計しなければうまく機能しない。そのため、半導体メーカーがチップレットの選定やパッケージの設計を一手に引き受けている。オープンチップレットがなかなか実現できない背景に、EDAツールの抱えている問題があるとソシオネクスト執行役員常務でプロダクション・クオリティマネジメントグループ長の内藤貢氏は指摘する。

チップレット集積では、チップレットを載せる中間基板(インターポーザー)や、インターポーザーを載せる基板が性能に大きな影響を及ぼす。そのため、チップレットだけではなく、インターポーザーや基板も含めたパッケージ全体の特性評価がEDAツールに必要になるのだ。実際、同社でチップレット集積向けのインターポーザーや基板を開発したところ、モノリシックチップの開発にはなかったような課題が出てきたという。

EDAツールベンダー側も「異なる種類のテクノロジーに対応できる設計ツールがない」(図研専務執行役員兼最高技術責任者で技術本部長の仮屋和浩氏)と、課題を認識している。例えば、チップレット集積では、異なるプロセスで造ったチップレットを1つのインターポーザーに載せる場合に、ツール上で仮想的に動作を検証できる機能が欠かせない。また、半導体の動作確認に用いるピン(端子)の数は、モノリシックチップでは30万〜50万個だったが、チップレットでは100万個以上になるとみられている。

「後工程には設計に踏み込んでいく文化がない」。チップレット集積を巡る開発体制の課題を指摘するのは、日本IBM東京基礎研究所セミコンダクターチップレット・インターコネクト部長の森裕幸氏だ。前工程ではデザインキット(設計情報)などを通して、ファウンドリー(受託製造)事業者側の事情を半導体の設計に落とし込む文化がある。一方で、後工程にそのような文化はないと同氏は語る。「チップレットの普及のためには、前工程のように後工程からも設計に関わっていくことが重要だ」(同氏)。ファウンドリー事業者が提供するPDK(プロセス・デザインキット)と、後工程用のADK(アセンブリー・デザインキット)が密接に連携して、初めてチップレットの最適化が実現できるようになる。

ダイレベルで良品保証

チップレット集積の課題として試験(テスト)を挙げるのは、愛媛大学大学院理工学研究科客員研究員の亀山修一氏だ。同氏は「チップレットではチップが封止される前のダイレベルの試験が重要になる」と話す。これは、大きな変化だ。従来のモノリシックチップで重要なのはパッケージング後の最終試験(ファイナルテスト)で、それによってチップは良品とされていた。

チップレット集積の場合、最終試験だけでは不十分だ。例えば、良品率が9割のチップレットを3つ組み合わせた場合、集積したパッケージの良品率は7割近くに下がる。そのため、従来のウエハーレベルの試験ではなく、ウエハーから小片化したダイレベルでの試験が重要になるというわけだ。最近では、ダイだけではなくマイクロバンプ(微細電極)の品質を確認する必要も出てきている。

日本企業は前工程技術のキャッチアップを

後工程の重要性が高まり、日本企業の材料や装置が脚光を浴びる中で、横浜国立大学大学院工学研究院システムの創生部門准教授の井上史大氏は日本企業に対して「前工程への理解が必要だ」と警鐘を鳴らす。

同氏は、チップレット集積などの先進パッケージングや、前工程と後工程が融合した「中工程」と呼ばれる領域について「後工程の中で前工程の技術が使われるようになる」と表現する。この新たな領域を巡って、前工程の企業は積極的に後工程に進出しようとしている。一方、後工程に強い日本企業の備えは十分でないという。

その一例が、今後の3次元(3D)実装で肝になるハイブリッドボンディング(ハイブリッド接合)だ。海外企業では、装置大手の米Applied Materials(アプライドマテリアルズ)などが積極的に開発を進めている。海外企業は「100〜200nmのパーティクル(微細なゴミ)に対応しなければいけないことを理解している」(同氏)。つまり、相対的に厳しい前工程並みの品質レベルで取り組もうとしている。一方、日本企業の中には、チップレット集積や中工程に対する品質レベルの認識が従来の後工程並みにとどまっているところがあるという。

キーワード

(NIKKEI Tech Foresight/日経クロステック 松元則雄)

0 コメント:

コメントを投稿